You can view and modify the CPU topologies of Elastic Compute Service (ECS) instances based on your business requirements to improve performance and parallelism and optimize resource allocation in various scenarios such as virtualization environments, multi-threaded programming, and high-performance computing (HPC). This topic describes how to call API operations to view and modify the CPU topologies of ECS instances.

Background information

Only specific Alibaba Cloud instance families support two types of CPU topologies: Hyper-Threading (HT) continuous (ContinuousCoreToHTMapping) CPU topology and HT discrete (DiscreteCoreToHTMapping) CPU topology.

HT continuous CPU topology: Logical cores are continuously assigned to physical cores, which can help reduce communication and contention between threads. This mode is suitable for computing tasks that require low memory access latency and computing power close to computing power provided by the physical cores, such as scientific computing, data analysis, and high-performance computing, which are sensitive to memory access and core computing.

HT discrete CPU topology: Logical cores are discretely distributed to physical cores, which can help reduce resource contention in a multi-threaded environment and provide better performance isolation. This mode is suitable for the tasks that are separately assigned to threads or the tasks that require high single-thread performance.

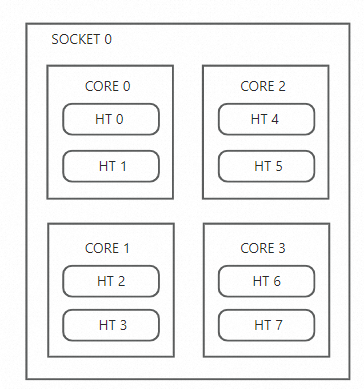

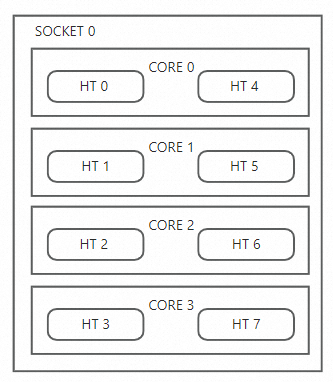

In this example, an x86 instance that has eight vCPUs is used. The following figures show the two types of CPU topologies.

The following figures show the two types of CPU topologies.

HT continuous CPU topology

Relationships between logical cores and physical cores:

HT 0andHT 1belong toCORE 0.HT 2andHT 3belong toCORE 1.HT 4andHT 5belong toCORE 2.HT 6andHT 7belong toCORE 3.

HT discrete CPU topology

Relationships between logical cores and physical cores:

HT 0andHT 4belong toCORE 0.HT 1andHT 5belong toCORE 1.HT 2andHT 6belong toCORE 2.HT 3andHT 7belong toCORE 3.

Limits

You can modify the CPU topologies of instances only in the following instance families:

ecs.g9i, ecs.c9i, and ecs.r9i

ecs.hfg9i, ecs.hfc9i, and ecs.hfr9i

ecs.g8i, ecs.c8i, and ecs.r8i

ecs.g7, ecs.c7, and ecs.r7

ecs.g7a, ecs.c7a, and ecs.r7a

ecs.hfg8i, ecs.hfc8i, and ecs.hfr8i

ecs.hfg7, ecs.hfc7, and ecs.hfr7

ecs.g6, ecs.c6, and ecs.r6

ecs.g6e, ecs.c6e, and ecs.r6e

For more information, see the Overview of instance families topic.

View CPU topologies

You can call the DescribeInstances operation with the AdditionalAttributes parameter and check the TopologyType response parameter for the CPU topology type of an instance. For more information, see DescribeInstances.

Valid values of the TopologyType parameter:

ContinuousCoreToHTMapping: HT continuous CPU topology.DiscreteCoreToHTMapping: HT discrete CPU topology.If the return value is empty, the CPU topology cannot be modified.

Modify the CPU topologies of instances

If you want to modify the CPU topology of an instance to meet your business requirements, we recommend that you perform benchmark tests and performance evaluation to determine the most suitable mode before you modify the CPU topology.

You can call an API operation and set the CpuOptions.TopologyType parameter to modify the CPU topology of an instance.

Modify the CPU topologies of instances during instance creation

Call the RunInstances operation and set the

CpuOptions.TopologyTypeparameter to modify the CPU topologies of instances. For more information, see RunInstances.Modify the CPU topology of an existing instance

NoteBefore you call an API operation to modify the CPU topology of an existing instance, make sure that the instance is in the Stopped state.

Call the ModifyInstanceAttribute operation and set the

CpuOptions.TopologyTypeparameter to modify the CPU topology of an existing instance. For more information, see ModifyInstanceAttribute.

Valid values of the CpuOptions.TopologyType parameter:

ContinuousCoreToHTMapping: HT continuous CPU topologyDiscreteCoreToHTMapping: HT discrete CPU topology